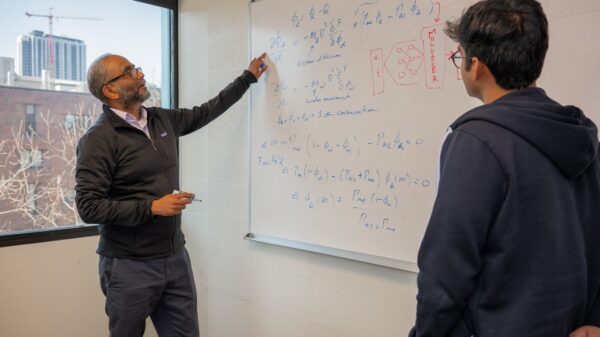

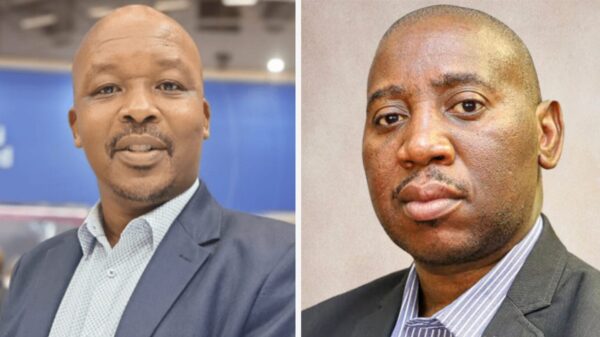

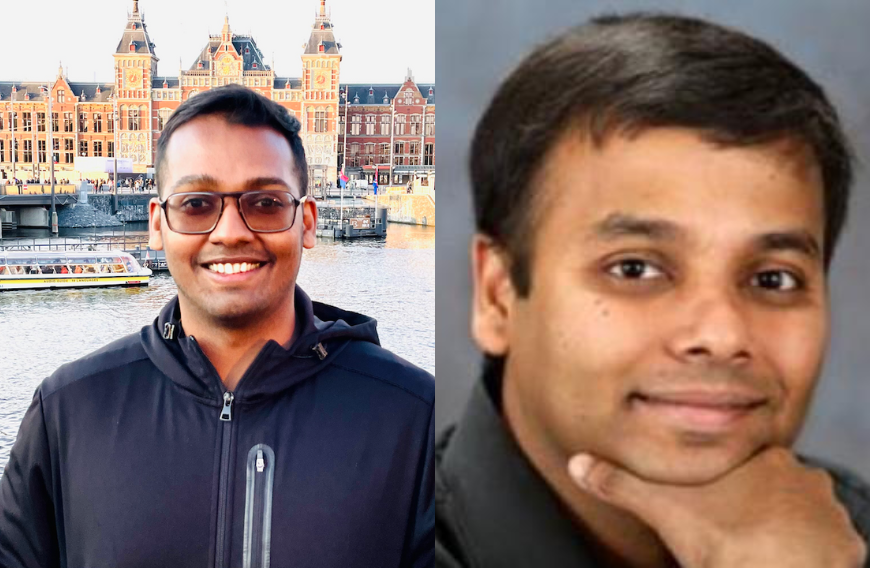

A team of engineers led by two Indian American professors has developed the first monolithic 3D chip produced in a U.S. foundry, achieving unprecedented wiring density and significant speed improvements. The milestone was detailed in a paper presented by Subhasish Mitra, the William E. Ayer Professor in Electrical Engineering and professor of computer science at Stanford University, at the 71st Annual IEEE International Electron Devices Meeting (IEDM). Tathagata Srimani, an assistant professor of electrical and computer engineering at Carnegie Mellon University and the paper’s senior author, initiated the project as a postdoctoral fellow under Mitra’s guidance.

Collaboration among engineers from Stanford University, Carnegie Mellon University, the University of Pennsylvania, and the Massachusetts Institute of Technology, alongside SkyWater Technology, the largest exclusively U.S.-based pure-play semiconductor foundry, has led to the creation of a novel multilayer chip. This architecture promises to pave the way for advancements in AI hardware and domestic semiconductor production.

Unlike traditional flat, 2D chips, the new prototype features ultra-thin components that rise vertically, resembling stories in a skyscraper. This design utilizes vertical wiring as high-speed data pathways, enabling rapid and extensive data transfer. The chip’s record-setting density of vertical connections, combined with its intricate integration of memory and computing units, allows it to avoid the bottlenecks that have hindered the performance of flat chip designs. Hardware tests indicate that this innovative 3D chip outperforms its 2D counterparts by a factor of four.

While experimental 3D chips have been developed in academic laboratories, this prototype stands out due to its clear performance gains and its manufacture in a commercial foundry. “This opens the door to a new era of chip production and innovation,” said Mitra. “Breakthroughs like this are how we get to the 1,000-fold hardware performance improvements future AI systems will demand.”

Modern AI models, such as ChatGPT and Claude, require massive data transfers between memory and the computing units responsible for processing. Conventional 2D chips are constrained by their single, flat architecture, forcing data to traverse longer distances along limited pathways. This scenario creates what engineers refer to as the “memory wall,” where processing speeds exceed the chip’s data delivery capabilities. Attempts to address this issue through transistor miniaturization are reaching physical limits, known as the “miniaturization wall.”

The new chip transcends these limitations by integrating memory and computation vertically, thus facilitating more efficient data movement. “By integrating memory and computation vertically, we can move a lot more information much quicker, just as the elevator banks in a high-rise let many residents travel between floors at once,” explained Srimani.

Initial hardware tests show that the prototype not only surpasses 2D chips but also lays the groundwork for future models with even greater capabilities. Simulations suggest that variants with additional stacked layers could offer up to a twelve-fold performance improvement on real AI workloads, especially those based on Meta’s open-source LLaMA model. Researchers assert that the design holds the potential for 100- to 1,000-fold enhancements in energy-delay product (EDP), a critical metric balancing speed and energy efficiency.

By significantly shortening data movement and increasing vertical pathways, the chip is positioned to achieve higher throughput while minimizing energy consumption per operation. This combination has long been considered difficult to achieve with conventional flat architectures. Beyond the immediate performance implications, the researchers highlight that this development marks a significant stride toward domestic hardware innovation. By demonstrating that monolithic 3D chips can be built in the U.S., this work sets a precedent for future advancement in chip design and manufacturing.

Mitra has been recognized with the Distinguished Alumnus Award from the Indian Institute of Technology, Kharagpur. Srimani holds both the SM and PhD degrees in Electrical Engineering and Computer Science from the Massachusetts Institute of Technology, as well as a B.Tech degree in Electronics and Communication Engineering from IIT Kharagpur.

See also Sai Sreenivas Kodur Reveals Strategies for Scalable, Reliable Enterprise AI Systems

Sai Sreenivas Kodur Reveals Strategies for Scalable, Reliable Enterprise AI Systems Alphabet Acquires Intersect for $4.75 Billion to Boost AI Infrastructure and Energy Solutions

Alphabet Acquires Intersect for $4.75 Billion to Boost AI Infrastructure and Energy Solutions Awiros Unveils Video AI Platform Powered by Intel for Enhanced Edge to Core Solutions

Awiros Unveils Video AI Platform Powered by Intel for Enhanced Edge to Core Solutions Nvidia to Deliver 40,000 H200 AI Chips to China by February 2026 Amid Export Controls

Nvidia to Deliver 40,000 H200 AI Chips to China by February 2026 Amid Export Controls Franchise Brands Utilize AI to Boost Marketing Efficiency and Drive Growth

Franchise Brands Utilize AI to Boost Marketing Efficiency and Drive Growth