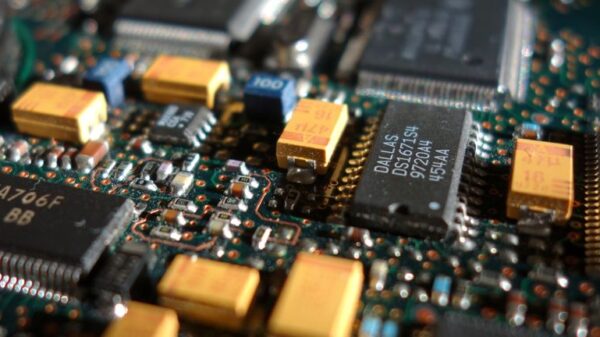

The semiconductor industry is experiencing a pivotal transformation as it shifts from traditional human-centric chip design to a new paradigm of “AI-defined” hardware, a change prominently showcased at CES 2026. Leading Electronic Design Automation (EDA) firms are demonstrating that integrating generative AI and reinforcement learning into the silicon lifecycle has become essential for survival in a rapidly evolving market. By automating complex design phases, these advanced tools are reducing development timelines from several months to mere weeks and significantly cutting prototyping costs by 20% to 60%.

This shift is particularly critical as the industry approaches the physical limits of Moore’s Law. Software intelligence is now providing a necessary tailwind, especially in sectors like automotive and high-performance computing, where the demand for customized, AI-optimized silicon is surpassing the capabilities of human engineering teams. The emergence of virtualized ecosystems and “agentic” design assistants is lowering the barriers to entry for custom silicon design, heralding a “Silicon Renaissance” that promises to propel innovation across various sectors of the global economy.

Central to the announcements at CES 2026 was the collaboration between Synopsys (Nasdaq: SNPS) and Arm (Nasdaq: ARM), which introduced the latest Virtualizer Development Kits (VDKs) optimized for the Arm Zena Compute Subsystem (CSS). This modular engineering feat includes a 16-core Arm Cortex-A720AE cluster and a dedicated “Safety Island” for real-time diagnostics. By utilizing Synopsys VDKs, automotive engineers can create a digital twin of the Zena hardware, enabling software teams to develop and test code for next-generation autonomous driving features well before the physical silicon is available—a process referred to as “shifting left.”

In a parallel showcase, Cadence Design Systems (Nasdaq: CDNS) highlighted its innovations in engineering virtualization through the Helium Virtual and Hybrid Studio. Cadence’s approach focuses on “Physical AI,” allowing for chiplet-based designs to be validated in a virtual environment that accurately mirrors the target hardware’s performance characteristics. Their collaborative ecosystem, which includes Samsung Electronics (OTC: SSNLF) and Arteris (Nasdaq: AIPRT), demonstrated how pre-validated chiplets can be assembled modularly, akin to Lego blocks. This modularity, coupled with Cadence’s Cerebrus AI, enables the autonomous optimization of “Power, Performance, and Area” (PPA), evaluating up to $10^{90,000}$ design permutations in a fraction of the time that traditional methods required.

One of the most striking metrics shared at the summit was the impact of generative AI on floorplanning, a complex process that once relied heavily on the expertise of senior engineers over months. Now, AI agents like Synopsys.ai Copilot are capable of producing optimized layouts in days by analyzing historical design data alongside real-time constraints. This advancement contributes to the notable 20-60% reduction in costs, resulting from fewer necessary design corrections and a diminished need for extensive engineering teams to manage routine optimization tasks.

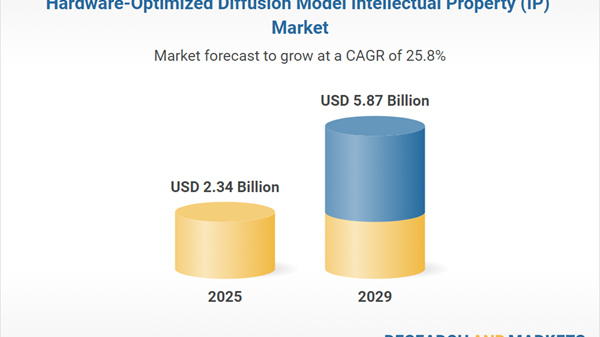

The democratization of high-end chip design through AI-driven EDA tools is reshaping the competitive landscape. Historically, only industry heavyweights like Nvidia (Nasdaq: NVDA) and Apple (Nasdaq: AAPL) possessed the resources to produce custom silicon. However, the cost reductions and accelerated timelines now enable mid-tier automotive original equipment manufacturers (OEMs) and startups to realistically pursue custom System on Chips (SoCs). This shift is redirecting power away from conventional chip manufacturers toward those capable of designing specialized hardware for targeted AI applications.

Cloud service providers are among the primary beneficiaries of this trend. Companies like Amazon (Nasdaq: AMZN) and Microsoft (Nasdaq: MSFT) are capitalizing on these AI-driven tools to expedite their internal silicon development, as seen with the Graviton and Maia series. By leveraging the “ISA parity” provided by the Arm Zena ecosystem, these hyperscalers create a seamless environment where code runs identically in both cloud and edge contexts, thereby reinforcing their dominance in the AI development pipeline.

Chip foundries and specialized manufacturers are also recalibrating their strategies. Firms such as NXP Semiconductors (Nasdaq: NXPI) and Texas Instruments (Nasdaq: TXN) have integrated Synopsys VDKs into their workflows to better serve the “Software-Defined Vehicle” (SDV) market. By offering virtual models of upcoming chips, they engage automotive manufacturers earlier in the design cycle, fostering a “virtual-first” sales model that positions the software environment as critical as the physical silicon, complicating competition for legacy players that lack robust AI-EDA strategies.

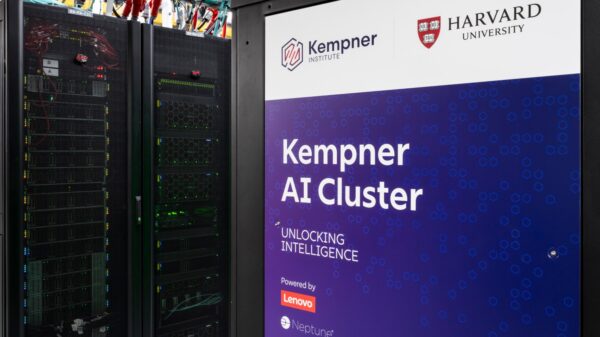

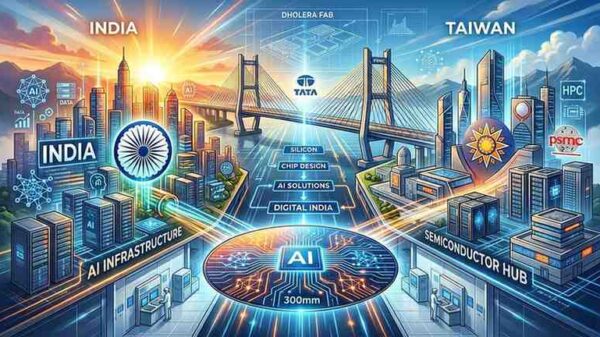

The implications of this transformation extend beyond technical advancements; they are geopolitical and economic milestones. In an era where nations are racing for “chip sovereignty,” the ability to design high-performance silicon locally without decades of manual engineering expertise is revolutionary. AI-led EDA tools act as a “force multiplier,” enabling smaller nations to establish viable semiconductor design sectors, potentially leading to a more decentralized global supply chain and reducing reliance on a select few design houses in Silicon Valley.

However, this rapid evolution raises concerns about the future of the semiconductor workforce. While the industry currently grapples with a talent shortage, the acceleration of design cycles suggests a shift in the role of human engineers towards high-level architectural oversight rather than direct hands-on optimization. Additionally, the complexities introduced by AI’s “black box” nature pose challenges regarding the security and verifiability of designs, particularly in mission-critical sectors like aerospace and healthcare.

As the industry considers its next steps, the horizon looms with the prospect of “Agentic EDA,” where AI systems will not only assist engineers but autonomously manage the entire design-to-manufacturing pipeline. Experts predict that by 2028, we may witness the first “lights-out” chip design projects, where all elements—from architectural specifications to final layout files—will be orchestrated by specialized AI agents capable of real-time adjustments based on manufacturing capacity and material costs.

The announcements from Synopsys, Cadence, and Arm at CES 2026 underscore AI’s emerging role as a cornerstone in shaping the digital future. The ability to condense lengthy design processes into weeks and cut costs significantly signals a permanent shift in technology development. This “Silicon Renaissance” ensures that as AI software continues to evolve, hardware efficiency will likewise soar, preventing a bottleneck in computational capabilities and setting the stage for unprecedented innovation in the years to come.

See also AI Automation Tools Drive Instant Digital Payouts, Reshaping User Expectations Across Industries

AI Automation Tools Drive Instant Digital Payouts, Reshaping User Expectations Across Industries AI Redefines Careers: How Workers Adapt and New Roles Emerge in 2023

AI Redefines Careers: How Workers Adapt and New Roles Emerge in 2023 Fundrise Launches RealAI, Analyzing 3.5 Trillion Data Points for $69/Month

Fundrise Launches RealAI, Analyzing 3.5 Trillion Data Points for $69/Month Adobe Enhances Photoshop with Firefly AI Tools for High-Resolution Image Editing

Adobe Enhances Photoshop with Firefly AI Tools for High-Resolution Image Editing OpenAI Reveals Human-Centered AI Strategy to Boost Employee Trust and Engagement

OpenAI Reveals Human-Centered AI Strategy to Boost Employee Trust and Engagement