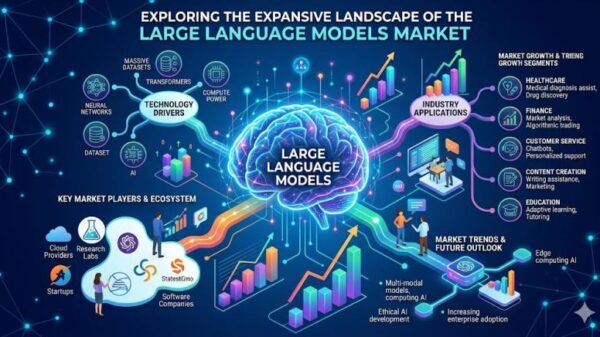

A recent study from Uppsala University has unveiled significant insights into the energy efficiency of Large Language Models (LLMs) through its technical paper titled “Prefill vs. Decode Bottlenecks: SRAM-Frequency Tradeoffs and the Memory-Bandwidth Ceiling.” Published in December 2025, the paper aims to address the critical factors influencing energy consumption in the deployment of LLMs, focusing on the intricate balance between on-chip SRAM size, operating frequency, and memory bandwidth.

The research underscores that energy consumption is a primary determinant of both the cost and environmental impact associated with LLMs. The authors—Hannah Atmer, Yuan Yao, Thiemo Voigt, and Stefanos Kaxiras—explore the roles of different operational phases in LLM inference, specifically the compute-bound prefill and memory-bound decode phases. Their findings suggest that the size of SRAM significantly affects total energy usage during both phases. However, while larger buffers provide increased capacity, they also contribute substantially to static energy consumption through leakage, a disadvantage that is not compensated for by corresponding latency improvements.

The researchers employed a combination of simulation methodologies—OpenRAM for energy modeling, LLMCompass for latency simulation, and ScaleSIM to assess operational intensity in systolic arrays. The results reveal a complex interaction between high operating frequencies and memory bandwidth limitations. While elevated frequencies can enhance throughput during the prefill phase by reducing latency, this benefit is significantly constrained during the decode phase due to memory bandwidth bottlenecks.

Interestingly, the study indicates that higher compute frequencies can paradoxically lead to reduced total energy consumption. This is achieved by shortening execution time, which minimizes static energy usage—more so than the increase in dynamic power that such frequencies typically elicit. The research identifies an optimal configuration for LLM workloads, suggesting that operating frequencies between 1200MHz and 1400MHz, paired with a compact local buffer size of 32KB to 64KB, yield the best energy-delay product. This balance is essential for achieving both low latency and high energy efficiency.

Moreover, the paper elucidates how memory bandwidth serves as a performance ceiling. The analysis demonstrates that performance gains from increased compute frequencies diminish once workloads transition from being compute-bound to memory-bound. These findings provide concrete architectural insights, showcasing paths for designing energy-efficient LLM accelerators, particularly relevant for data centers striving to reduce energy overhead.

As the demand for energy-efficient AI models continues to rise, this research highlights the pivotal role of hardware configuration in optimizing performance while minimizing environmental impact. The integration of advanced simulation techniques and a detailed understanding of phase behaviors stands to inform future architectural designs, potentially transforming energy management strategies in AI applications.

See also Ngee Ann Polytechnic Integrates Generative AI into Curriculum for All Students by 2026

Ngee Ann Polytechnic Integrates Generative AI into Curriculum for All Students by 2026 TurboDiffusion Achieves 200x Faster Video Generation, Revolutionizing Content Creation

TurboDiffusion Achieves 200x Faster Video Generation, Revolutionizing Content Creation Kakao Reveals Kanana-v-4b-Hybrid AI Model with Enhanced Multimodal Capabilities

Kakao Reveals Kanana-v-4b-Hybrid AI Model with Enhanced Multimodal Capabilities MiniMax Prices Hong Kong IPO at HK$165, Aiming for US$538M amid AI Boom

MiniMax Prices Hong Kong IPO at HK$165, Aiming for US$538M amid AI Boom