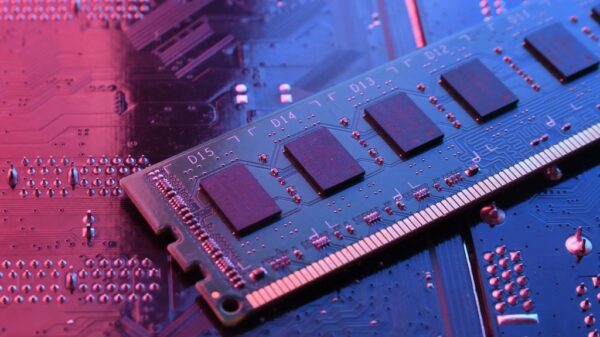

Researchers at Stanford University have unveiled a breakthrough in chip design that could significantly enhance the performance of artificial intelligence (AI) systems. In a study released in December 2025, they demonstrated how a new type of 3D computer chip can effectively alleviate a longstanding bottleneck in AI processing: the slow movement of data across chip surfaces.

Traditional computer chips often have components arranged flatly, which creates significant distance between memory and processing units. This physical separation can lead to substantial delays, particularly as modern AI models require rapid data exchanges. The phenomenon is referred to as the “memory wall,” where processing units, despite their speed, idle while awaiting data. As transistors shrink and approach physical limits, known as the miniaturization wall, this issue has become increasingly pronounced.

The innovative design by the Stanford research team stacks memory and computing components vertically, rather than horizontally. This approach allows for closer proximity between data and processing units, which can significantly reduce delays. The researchers explained that they employed a method known as monolithic 3D integration, which facilitates more connections and tighter packing by constructing each layer directly on top of the last in a continuous manufacturing process.

In preliminary tests, the new chip outperformed traditional flat designs by a factor of four, and simulations suggest that as more layers are added, performance could increase by as much as twelve times for real AI workloads. “This opens the door to a new era of chip production and innovation,” stated Subhasish Mitra, a professor at Stanford involved in the research. “Breakthroughs like this are how we get to the 1,000-fold hardware performance improvements future AI systems will demand.”

While 3D chip designs are not entirely novel, previous attempts typically involved stacking separate chips, which still created choke points in data transfer. The Stanford team’s approach seeks to resolve these issues, which could pave the way for better scalability in production. Notably, the chip was manufactured in a commercial US foundry, underscoring its potential for widespread adoption.

The implications of this research extend beyond mere speed enhancements. By minimizing the distance data must travel and reducing the energy consumed per operation, the architecture is poised to deliver substantial efficiency gains. As AI systems continue to grow in sophistication and energy demands, this vertical chip design could be pivotal in shaping the next generation of AI hardware.

The Stanford researchers envision a future where such innovations can fundamentally alter the landscape of computing, leading to faster, more efficient devices capable of tackling the increasingly complex demands of AI applications. This development marks a significant step toward addressing the critical challenges facing AI hardware, potentially enabling many of the advancements that have been long anticipated in the field.

For further information, you can visit the official Stanford University website.

China’s DeepSeek R1 Disrupts U.S. AI Strategy, Sparks Techno-Nationalism and Global Backlash

China’s DeepSeek R1 Disrupts U.S. AI Strategy, Sparks Techno-Nationalism and Global Backlash Nvidia’s $20B Licensing Deal with Groq Reinforces AI Dominance Amid Growing Competition

Nvidia’s $20B Licensing Deal with Groq Reinforces AI Dominance Amid Growing Competition Vitalik Buterin Endorses Grok’s Role in Enhancing Truth Discovery on X Amid AI Bias Concerns

Vitalik Buterin Endorses Grok’s Role in Enhancing Truth Discovery on X Amid AI Bias Concerns Oracle Faces 30% Stock Plunge Amid Delays in $400B OpenAI Data Center Projects

Oracle Faces 30% Stock Plunge Amid Delays in $400B OpenAI Data Center Projects