Artificial intelligence hardware is evolving, with manufacturers pushing the boundaries on size, electrical density, and material complexity. At the forefront of this evolution is TSMC’s CoWoS technology, which facilitates the Chip on Wafer on Substrate packaging method. This advanced technique allows for the integration of multiple semiconductor dies and high-bandwidth memory stacks on a large silicon interposer, significantly increasing computational density.

However, as the industry embraces these high-density designs, a critical question looms: does this increased density lead to a reduced critical mineral footprint per unit of useful AI compute? This challenge parallels the development of exascale supercomputers and AI datacenters, where facilities consuming multi-megawatts of power are testing their limits against environmental constraints and grid demands.

Achieving sustainable outcomes is far from guaranteed. While CoWoS can contribute to sustainability under certain configurations, it can also raise the embodied silicon and metal intensity within the package. The true measure of sustainability hinges on factors beyond just packaging density; yield, chiplet architecture, system efficiency, and lifecycle design play pivotal roles. These elements are crucial in a global competition for vital technology, as access to minerals and advanced packaging capabilities increasingly dictates who can deploy cutting-edge AI hardware effectively.

Decoding Critical Mineral Intensity and Silicon Interposers

Understanding the metric of “critical mineral intensity per compute” is essential for grasping the environmental implications of advanced packaging. This metric essentially measures the quantity of critical minerals embedded in an accelerator package, including its memory and packaging structures, divided by the useful compute over its lifespan.

The U.S. government updated its strategic mineral designations in November 2025, adding materials like copper, silicon, silver, and tin due to their economic significance and vulnerability within supply chains. These materials are vital for energy systems, electronics, and semiconductor infrastructure, emphasizing the importance of mineral risk assessment in global supply chains.

High-density packaging necessitates meticulous material accounting to understand environmental impact. CoWoS incorporates essential materials now central to the global supply chain: silicon serves as the primary substrate, copper forms the electrical pathways, while silver and tin enable reliable solder joints. Nickel and cobalt are also key as barrier layers within package structures. Therefore, credible sustainability claims must consider both the total silicon area and the cumulative metal density within the complete module.

The reality dispels the misconception that denser hardware requires fewer materials. The demand for materials is influenced by the specific methods employed to achieve density and their impact on overall system demand.

CoWoS represents a paradigm shift in packaging architecture by allowing multiple chips to work as a cohesive system. Rather than merely reducing chip size, it enables tight integration of processors and memory stacks on a silicon interposer, effectively acting as a miniature printed circuit board with finely structured interconnections. Technical specifications indicate that CoWoS S can accommodate a silicon interposer up to about 2,700 square millimeters, providing substantial additional area for interconnection.

This distinction is critical, as CoWoS does not inherently shrink die size; rather, it facilitates the integration of logic and memory with short electrical paths, and may enable chiplet designs. However, this packaging architecture introduces extra silicon area that requires dedicated resources for fabrication and supply chains, and the environmental outcome relies on the architectural choices that follow.

A 300-millimeter wafer, which has around 70,686 square millimeters of usable area, faces challenges as large interposers, such as those enabled by CoWoS, can consume more silicon overall, especially if the dimensions of logic dies remain unchanged. When large interposers are introduced, fewer can fit on a wafer, thus increasing material usage.

This trend highlights a significant point: while CoWoS can theoretically increase wafer starts without reducing logic die sizes, it also consumes a considerable portion of each wafer. Detailed wafer-utilization models show how shifts in wafer demand can ripple through global manufacturing, emphasizing the need for rigorous sustainability analysis that avoids simplistic marketing claims.

The core sustainability advantage of CoWoS rests in its flexibility, facilitating chiplet designs that enhance yield. Smaller dies statistically yield better outcomes, minimizing wasted wafers and potentially reducing the total wafer starts needed for specific compute outputs. When coupled with chiplet architectures, CoWoS can act as a high-density wiring platform, which may result in reduced mineral demands when optimized correctly.

Yet, without yield improvements or chiplet optimizations, CoWoS alone does not assure mineral savings. The advanced packaging redistributes material intensity, increasing localized density of key elements like silicon, copper, and silver across the package. These metals, now classified as critical in the U.S., necessitate careful scrutiny of the overall material footprint.

As the demand for data centers grows, energy efficiency becomes paramount. The sustainability metrics now focus on energy per useful inference and overall compute delivered over the service life of the hardware. If CoWoS-enabled accelerators can complete workloads efficiently or replace multiple older units, overall infrastructure demand may decrease, counterbalancing the higher mineral intensity at the system level.

With challenges in lifecycle recovery and the complexities of recycling materials from multi-die assemblies, the industry must prioritize yield optimization, system efficiency, and enhanced circularity. Only by refining the sustainability calculus behind advanced packaging can the industry hope to create hardware that is both powerful and environmentally responsible.

See also Nvidia Projects 60-120% Stock Increase Over Next 5 Years Amid AI Growth

Nvidia Projects 60-120% Stock Increase Over Next 5 Years Amid AI Growth Yogi Adityanath Launches IBM AI GovTech Innovation Centre to Propel Quantum Computing in Uttar Pradesh

Yogi Adityanath Launches IBM AI GovTech Innovation Centre to Propel Quantum Computing in Uttar Pradesh Local Engineers Leverage AI Tools to Enhance Productivity by 30% and Streamline Workflows

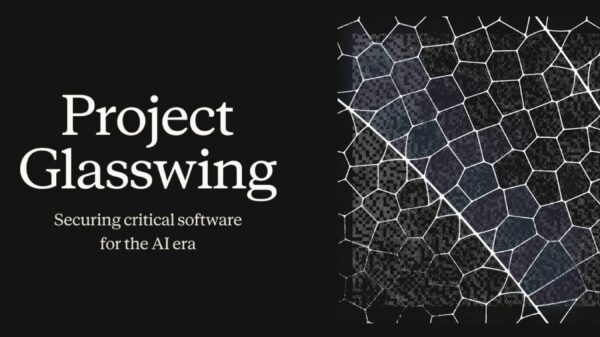

Local Engineers Leverage AI Tools to Enhance Productivity by 30% and Streamline Workflows Microsoft Report Reveals Urgent Need for Scalable Media Authentication Against AI Manipulation

Microsoft Report Reveals Urgent Need for Scalable Media Authentication Against AI Manipulation AI Professionals Must Cultivate Human Quota (HQ) to Thrive in Tech-Dominated Future

AI Professionals Must Cultivate Human Quota (HQ) to Thrive in Tech-Dominated Future